Analysis and Design of System-on-Chip——Course Notes

Personal Learning Notes for the Course: Analysis and Design of System-on-Chip at BUPT.

SoC课笔记,简略PPT,扩展重要内容

评分规则

- 课堂10% + 平时作业45% + 期末课程设计45%

参考书

- 《SoC设计方法与实现(第4版)》 魏继增等

第一章 SoC概述

什么是集成电路?

- 芯片从下线到最终应用所经历的各个环节:晶圆与裸片->封装->芯片成品->方案与系统->终端产品

集成电路内部是啥?

- 集成电路内部包含几万至几百亿支晶体管

这么复杂,怎么做?

- 交叉性很强,涵盖材料、器件、电路、软件、工艺、制造

水泥:器件、CMOS标准单元、设计规则

图纸:功能定义、RTL、网表和版图

施工:制造、封装、测试

集成电路设计的任务

- 借助EDA,在不同抽象层次描述设计,完成从SPEC到GDSII

- 顶层:SPEC(需求规格) 设计的起点,是对芯片功能、性能(如速度、功耗)、接口的文字 / 图表定义(如 “实现某型号处理器的运算单元,支持 1GHz 频率,功耗≤50mW”),不涉及任何电路细节。

- 抽象层次 1:算法 / 架构级(最高层) 用工具将 SPEC 转化为架构方案,比如确定运算单元用 “流水线架构” 还是 “并行架构”,明确模块划分(如运算器、控制器、寄存器组),验证架构是否满足性能需求。

- 抽象层次 2: RTL 级(寄存器传输级) 用硬件描述语言(如 Verilog、VHDL)描述各模块的逻辑功能,比如 “当输入信号 A 为高时,寄存器 B 的数据传输到运算器 C”,本质是定义 “数据在寄存器间的传输逻辑”,这是设计的核心抽象层,EDA 工具会在此阶段做逻辑仿真验证(确保逻辑正确)。

- 抽象层次 3:门级(逻辑级) 通过 EDA 工具的 “逻辑综合”,将 RTL 代码转化为具体的 “门电路组合”(如与门、或门、触发器),并映射到特定工艺库(Foundry 提供的标准化门电路单元),同时优化时序(确保信号传输速度达标)、功耗。

- 抽象层次 4:物理级(底层) 基于门级网表,用 EDA 工具完成 “物理实现”:先做 “布局”(将所有门电路单元放在芯片版图的合理位置),再做 “布线”(用金属线连接各单元的引脚,满足电气规则),最终生成GDSII 格式文件—— 这是物理版图的标准格式,包含芯片所有物理层(金属层、介质层、掺杂层)的图形数据,可直接交付 Foundry 用于光刻生产。

第一节 集成电路概述

- 目的:实现电路和系统的集成。

- 对应的产业:半导体行业——以半导体材料为加工对象。

- 核心产品:集成电路

集成电路的定义: 即芯片,通过一系列特定的加工工艺,将晶体管、二极管等有源器件和电阻电容等无源器件,按照一定的电路互联,“集成”在一块半导体单晶片上,封装在一个外壳内,执行特定的电路或系统功能。

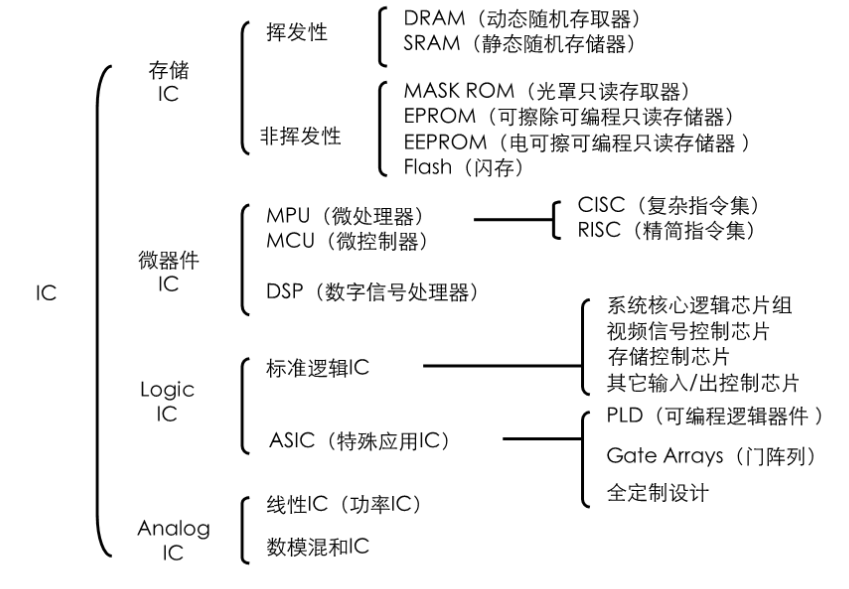

IC的分类

第二节 集成电路发展历史

- 1947年,美国贝尔实验室发明第一个晶体管

- 1958年,杰克·基尔比做出世界上第一块集成电路 其余略

摩尔定律

- “在价格不变的情况下,集成电路上可容纳的元器件数量约每隔18-24个月便会增加一倍,同时性能也将提升一倍。”

为什么说摩尔定律快要终结了?

- 集成度、性能、功耗、成本的等摩尔定律的特征不再统一提升或缩减:

- 晶体管尺寸逐渐接近物理极限,继续缩小会遇到量子隧穿效应、漏电流增加等问题;

- 传统存算架构面临能效瓶颈,算的速度大于存的速度;

- 电子迁移率退化限制器件速度的提升;

- 后道互连线的寄生效应主导系统延迟;

- 互连延迟超过晶体管的延迟。

后摩尔时代三大技术路线

More Moore(延续摩尔):“把传统路走到底” 不脱离摩尔定律的核心逻辑,继续通过 “缩小晶体管尺寸” 提升芯片性能、降低成本,是对传统技术路线的深化而非颠覆。

More than Moore(超越摩尔):“把单芯片做‘杂’” 不再只追求 “晶体管密度”,而是聚焦 “功能集成”—— 在同一芯片或封装内,将不同功能的器件(如逻辑电路、射频、传感器、功率器件、MEMS 微机电系统等)整合,实现 “1+1>2” 的系统级价值。

Beyond Moore / Beyond CMOS(超越 CMOS):“换条路重新走” 彻底跳出传统 “CMOS 晶体管(互补金属氧化物半导体)” 的框架,探索基于全新物理原理、材料或器件结构的 “非 CMOS 技术”,本质是 “用新底层技术替代传统路线”,解决 CMOS 面临的物理极限(如量子效应、功耗墙)。

第三节 集成电路产业分工

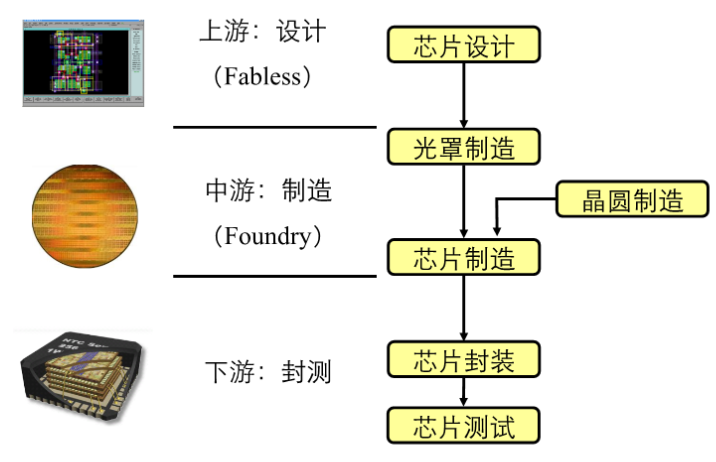

集成电路产业链

- 上游是设计(Fabless):负责芯片设计,企业根据需求设计电路与系统功能;

- 中游是制造(Foundry):负责光罩、晶圆、芯片制造,把设计转化为实际芯片;

- 下游是封测:负责芯片封装和测试,将制造好的裸片封装成可用芯片,并进行测试。

第四节 什么是SoC?

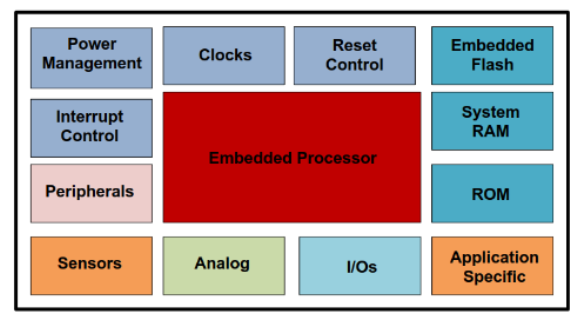

- SoC:System-on-Chip 片上系统 一个芯片就是一个系统,将系统的主要功能(处理器内核、存储器、外设等)集成到一个芯片上,由功能单一、固定的芯片,变成系统软硬件解决方案

SoC的特点

- 先有系统,才有SoC芯片(考虑集成更多功能)

- 功能复杂,芯片规模大

- 专用属性更强

- 基于IP的设计方法

IP: Intelligent Property ,直译为“知识产权”,在IC领域定义为:具有知识产权的,经过反复验证为正确的集成电路模块。IP核(IP core )还分为软核,固核,硬核,主要是根据不同的应用或者设计层次来分类的。一般来说软核价格更高,可维护性性和重用性强,为高层Verilog HDL或VHDL模型;固核为电路网表文件,硬核为电路结构版图掩摸,性能稳定但不宜修改。

SoC的优势

- 成本更低

- 高可靠性

- 系统体积大幅降低

- 系统软硬件开发难度大幅降低

- 高性能、低成本、低功耗,PPA全方位优势

SoC现状

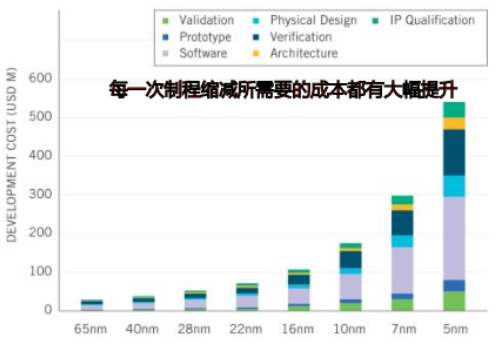

- 分久必合,合久必分 在近些年来不断的制程缩减中显露颓势:

- 趋近工艺极限时,收益下降

- NRE成本高

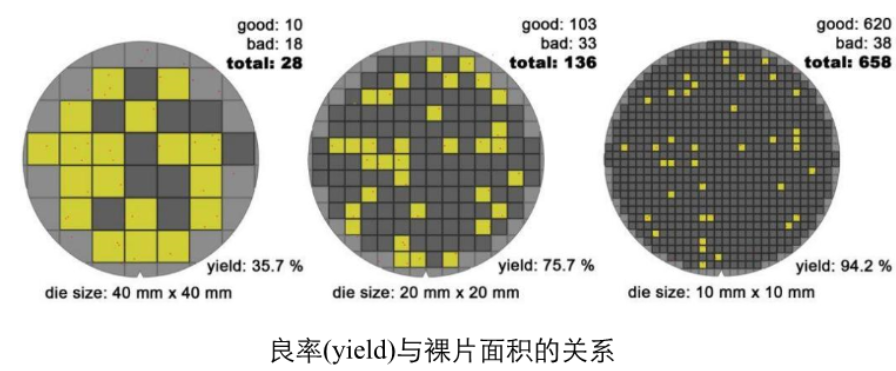

- 本身因为芯片规模大,良率下降,成本增加

- 受不同模块工艺需求不同的影响,难以协调。